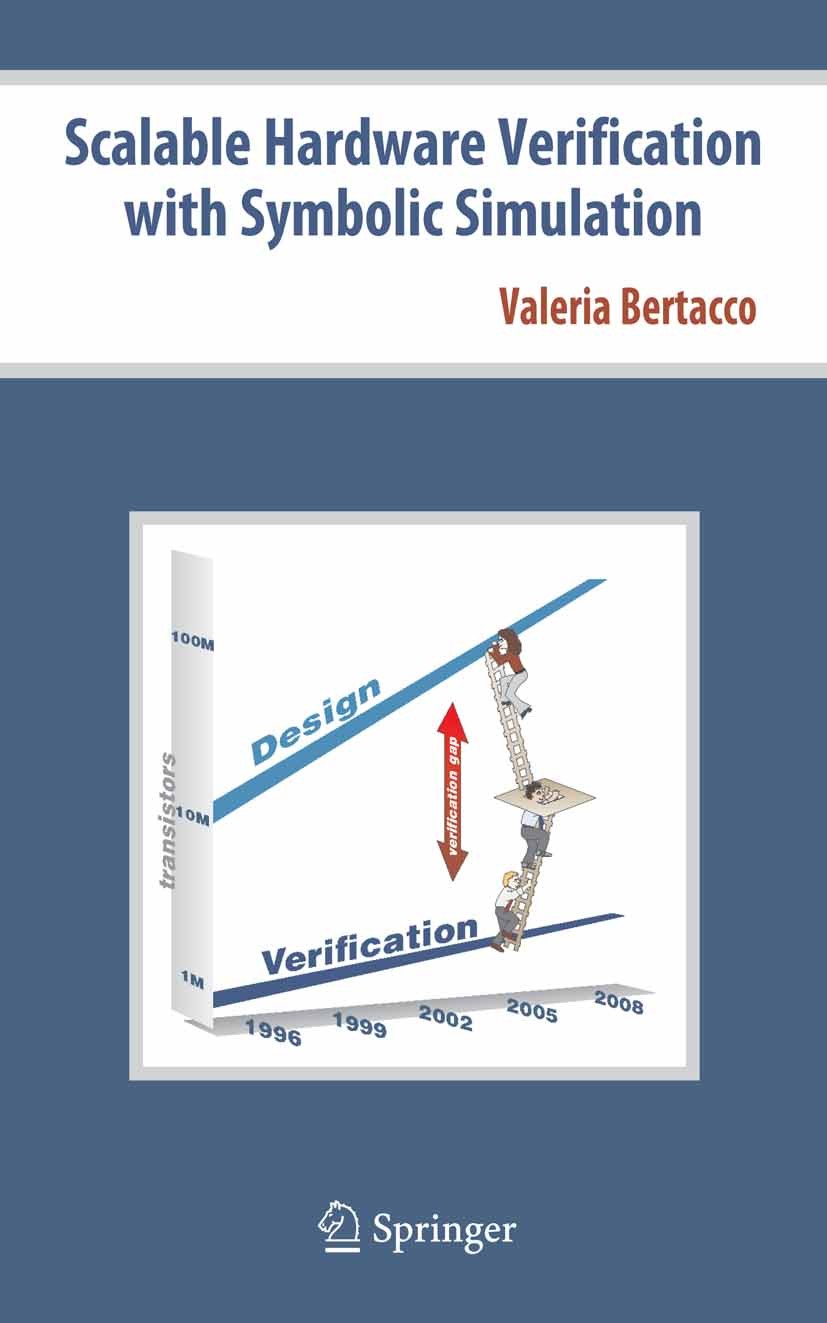

| 书目名称 | Scalable Hardware Verification with Symbolic Simulation | | 编辑 | Valeria Bertacco | | 视频video | http://file.papertrans.cn/862/861032/861032.mp4 | | 概述 | An innovative presentation of the theory of disjoint support decomposition, presenting novel results and algorithms, plus original and up-to-date techniques in formal verification.Provides an overview | | 图书封面 |  | | 描述 | .Scalable Hardware Verification with Symbolic Simulation. presents recent advancements in symbolic simulation-based solutions which radically improve scalability. It overviews current verification techniques, both based on logic simulation and formal verification methods, and unveils the inner workings of symbolic simulation. The core of this book focuses on new techniques that narrow the performance gap between the complexity of digital systems and the limited ability to verify them. In particular, it covers a range of solutions that exploit approximation and parametrization methods, including quasi-symbolic simulation, cycle-based symbolic simulation, and parameterizations based on disjoint-support decompositions....In structuring this book, the author’s hope was to provide interesting reading for a broad range of design automation readers. The first two chapters provide an overview of digital systems design and, in particular, verification. Chapter 3 reviews mainstream symbolic techniques in formal verification, dedicating most of its focus to symbolic simulation. The fourth chapter covers the necessary principles of parametric forms and disjoint-support decompositions. Chapters | | 出版日期 | Book 2006 | | 关键词 | CAD; Hardware; algorithms; automation; complexity; computer; computer-aided design (CAD); design automation | | 版次 | 1 | | doi | https://doi.org/10.1007/0-387-29906-8 | | isbn_softcover | 978-1-4419-3739-1 | | isbn_ebook | 978-0-387-29906-8 | | copyright | Springer-Verlag US 2006 |

The information of publication is updating

|

|

|Archiver|手机版|小黑屋|

派博传思国际

( 京公网安备110108008328)

GMT+8, 2025-12-16 08:03

|Archiver|手机版|小黑屋|

派博传思国际

( 京公网安备110108008328)

GMT+8, 2025-12-16 08:03